無刷電機BLDC驅動控制硬件電路分享

2020/8/7 10:19:02 點擊:

大家在工作中,經常會遇到硬件、軟件配合不愉快,影響工作效率,小編今天結合我們現有硬件經驗,給的大家分享,共同探討一下無刷電機驅動控制硬件注意事項和參考電路。

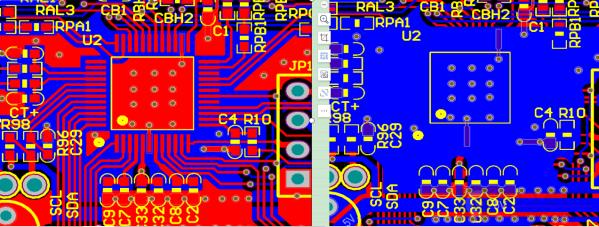

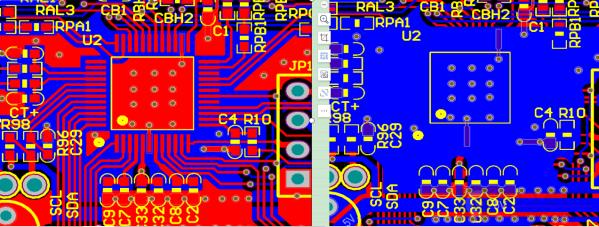

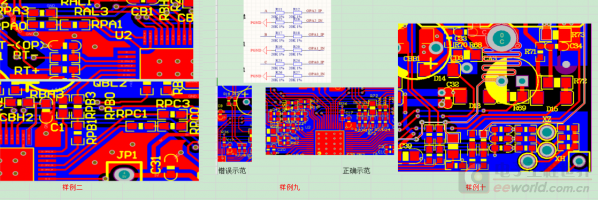

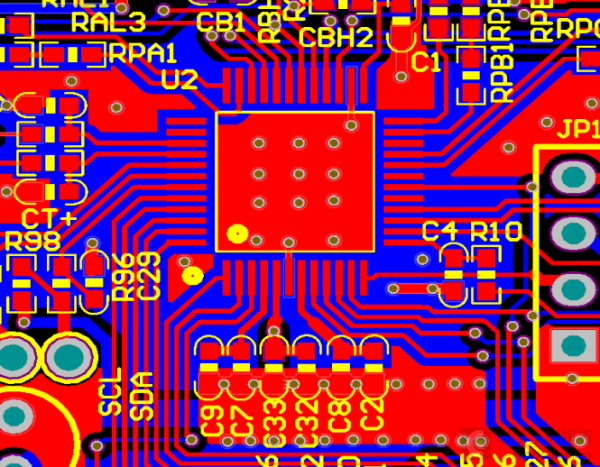

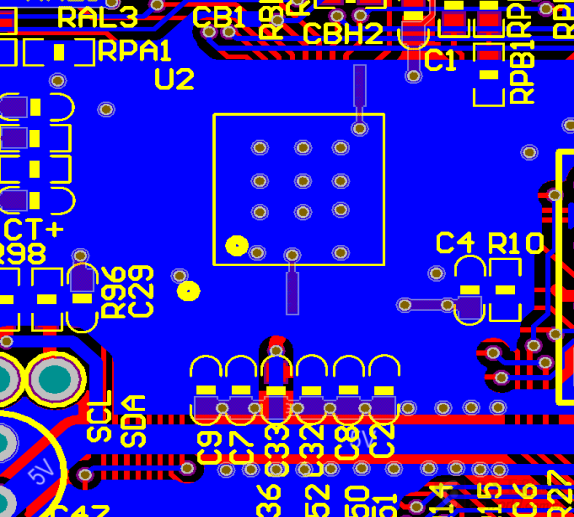

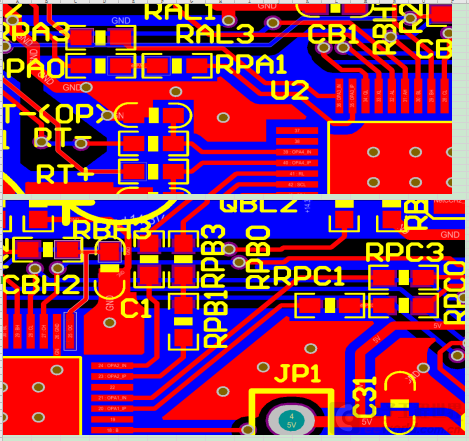

一,1,芯片背面的最好不要走線,保持地線覆銅的完整性,(參見樣例一)。

2,電源線寬度在20mil以上。

3,所有信號線必須在經過去耦、濾波電容之后才能進入相應的元器件管腳,不能將去耦、濾波電容放置在一旁。

(樣例一)

二,1,AVDD管腳處接一個大于或等于1uF瓷片去耦電容。

2,AVDD管腳到去耦電容之間的距離小于2cm(參見樣例一)。

3,AVDD管腳到去耦電容連接線之間沒有過孔。

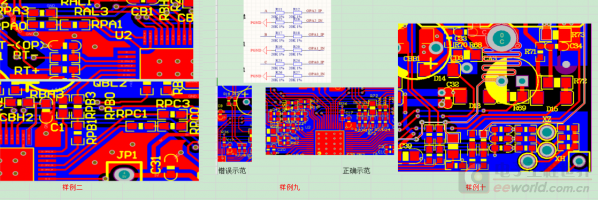

三,1,運放輸入端的匹配電阻距離芯片引腳應小于2cm(參見樣例二),并且兩組電阻不能分開(參加樣例九)。

2,運放輸入端的匹配電阻連接到相應MOS管源極和漏極(或采樣電阻兩端)的引線應走差分線,不可以就近選擇系統地線(參見樣例十)。

3,運放輸入端及連接的匹配電阻到最終的采樣電阻之間的走線,就盡可能減少過孔的數量(參見樣例十)。

四,1,AVDD的去耦電容接地端、RESET的復位電路電容接地端,與芯片的地(AVSS)之間圍成的區域是全部覆地(在芯片背面),該區域圍成的地沒有被其他走線分割(參見樣例一)。

2,RESET的RC復位電路距離芯片1cm以內(參見樣例一)

3,PCB頂層和底層的覆地,每平方厘米內過孔5個以上(參見樣例一)。

4,AVDD/RESET濾波電容的接地端需通過2個以上的過孔打到背面的大面積覆地,芯片地需通過6個以上過孔到背面覆地。

5,開關電源部分不能覆地,大面積敷地和開關電源部分保持至少3mm的距離。

五,1,過孔內徑不小于15mil。

2,芯片的所有模擬輸入端不能懸空,例如OPA_IP OPA_IN等,不使用時需將其接地。

3,信號線和地線上不可串磁珠。

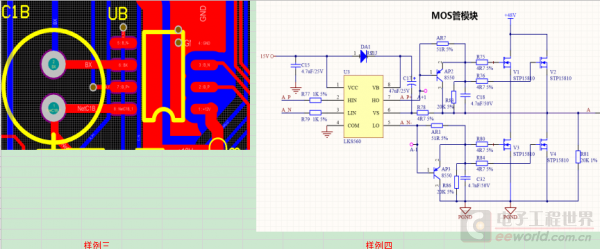

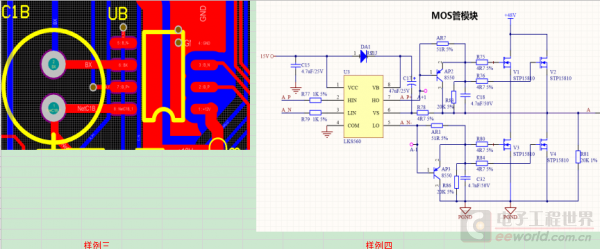

六,1,使用集成預驅動芯片的設計,集成預驅動芯片的GND引腳通過過孔接地的,至少使用兩個過孔(參見樣例三)。

2,使用集成預驅動芯片的設計,集成預驅動芯片的VCC引腳通過過孔接電源的,至少使用兩個過孔。

3,使用集成預驅動芯片的設計,為減少信號反射,預驅芯片的兩個輸入端需要加一個1K電阻(參見樣例四)。

4,預驅芯片的VS端要先經過Boost電容再到相線,PCB上需要走蛇形線,形成一個小電感,用來降低相線較大的dV/dt對預驅芯片的影響(參見樣例八)。

一,1,芯片背面的最好不要走線,保持地線覆銅的完整性,(參見樣例一)。

2,電源線寬度在20mil以上。

3,所有信號線必須在經過去耦、濾波電容之后才能進入相應的元器件管腳,不能將去耦、濾波電容放置在一旁。

(樣例一)

二,1,AVDD管腳處接一個大于或等于1uF瓷片去耦電容。

2,AVDD管腳到去耦電容之間的距離小于2cm(參見樣例一)。

3,AVDD管腳到去耦電容連接線之間沒有過孔。

三,1,運放輸入端的匹配電阻距離芯片引腳應小于2cm(參見樣例二),并且兩組電阻不能分開(參加樣例九)。

2,運放輸入端的匹配電阻連接到相應MOS管源極和漏極(或采樣電阻兩端)的引線應走差分線,不可以就近選擇系統地線(參見樣例十)。

3,運放輸入端及連接的匹配電阻到最終的采樣電阻之間的走線,就盡可能減少過孔的數量(參見樣例十)。

四,1,AVDD的去耦電容接地端、RESET的復位電路電容接地端,與芯片的地(AVSS)之間圍成的區域是全部覆地(在芯片背面),該區域圍成的地沒有被其他走線分割(參見樣例一)。

2,RESET的RC復位電路距離芯片1cm以內(參見樣例一)

3,PCB頂層和底層的覆地,每平方厘米內過孔5個以上(參見樣例一)。

4,AVDD/RESET濾波電容的接地端需通過2個以上的過孔打到背面的大面積覆地,芯片地需通過6個以上過孔到背面覆地。

5,開關電源部分不能覆地,大面積敷地和開關電源部分保持至少3mm的距離。

五,1,過孔內徑不小于15mil。

2,芯片的所有模擬輸入端不能懸空,例如OPA_IP OPA_IN等,不使用時需將其接地。

3,信號線和地線上不可串磁珠。

六,1,使用集成預驅動芯片的設計,集成預驅動芯片的GND引腳通過過孔接地的,至少使用兩個過孔(參見樣例三)。

2,使用集成預驅動芯片的設計,集成預驅動芯片的VCC引腳通過過孔接電源的,至少使用兩個過孔。

3,使用集成預驅動芯片的設計,為減少信號反射,預驅芯片的兩個輸入端需要加一個1K電阻(參見樣例四)。

4,預驅芯片的VS端要先經過Boost電容再到相線,PCB上需要走蛇形線,形成一個小電感,用來降低相線較大的dV/dt對預驅芯片的影響(參見樣例八)。

- 上一篇:電機缺相運行分析及其原因 2020/8/7

- 下一篇:Allegro全新高級霍爾效應電流傳感器可支持更高的電流和帶 2020/8/7